A Reconfigurable Spatial Array for Spectrally Agile Wireless Processing (2025)

You can find the full paper Here.

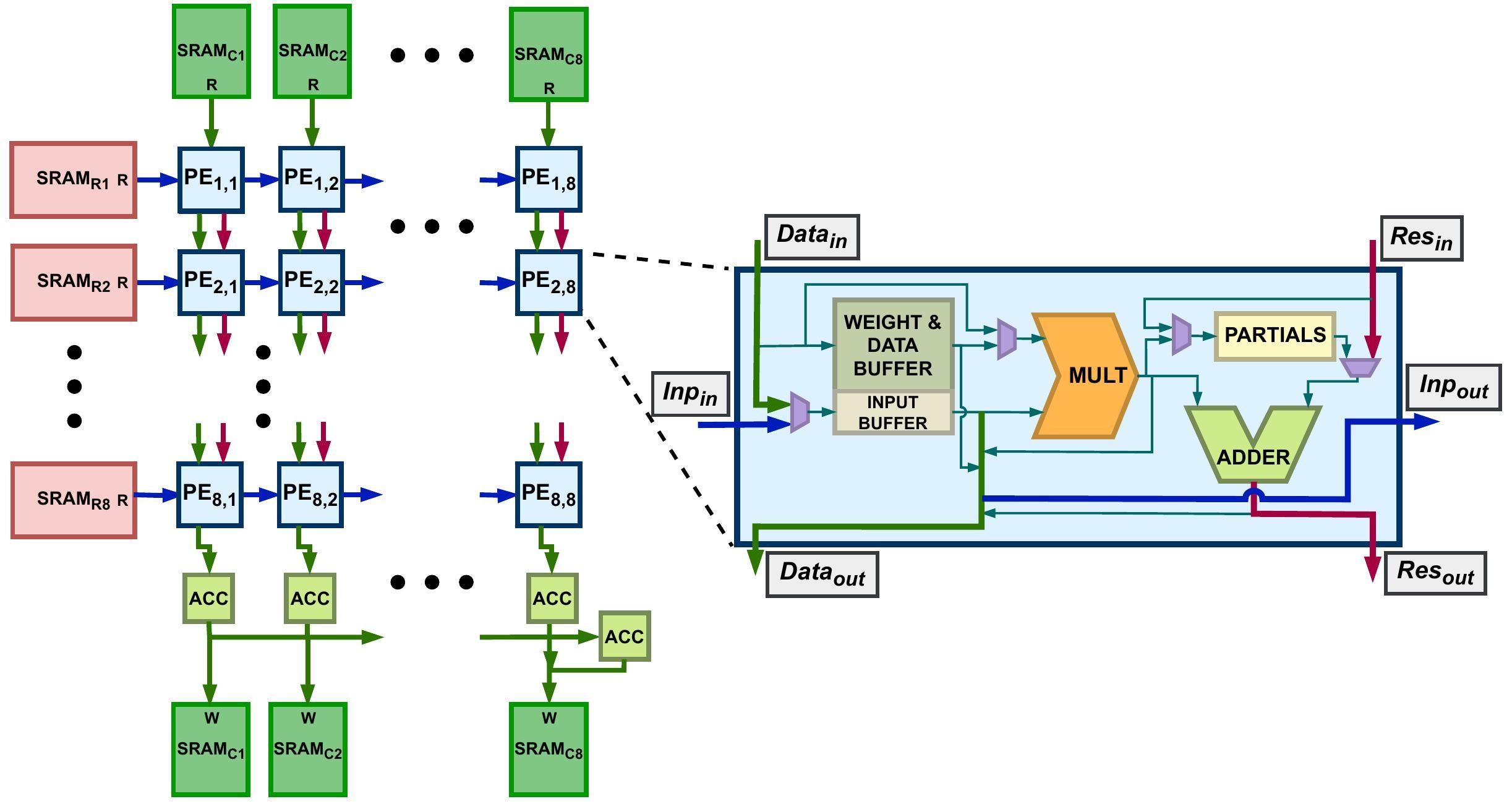

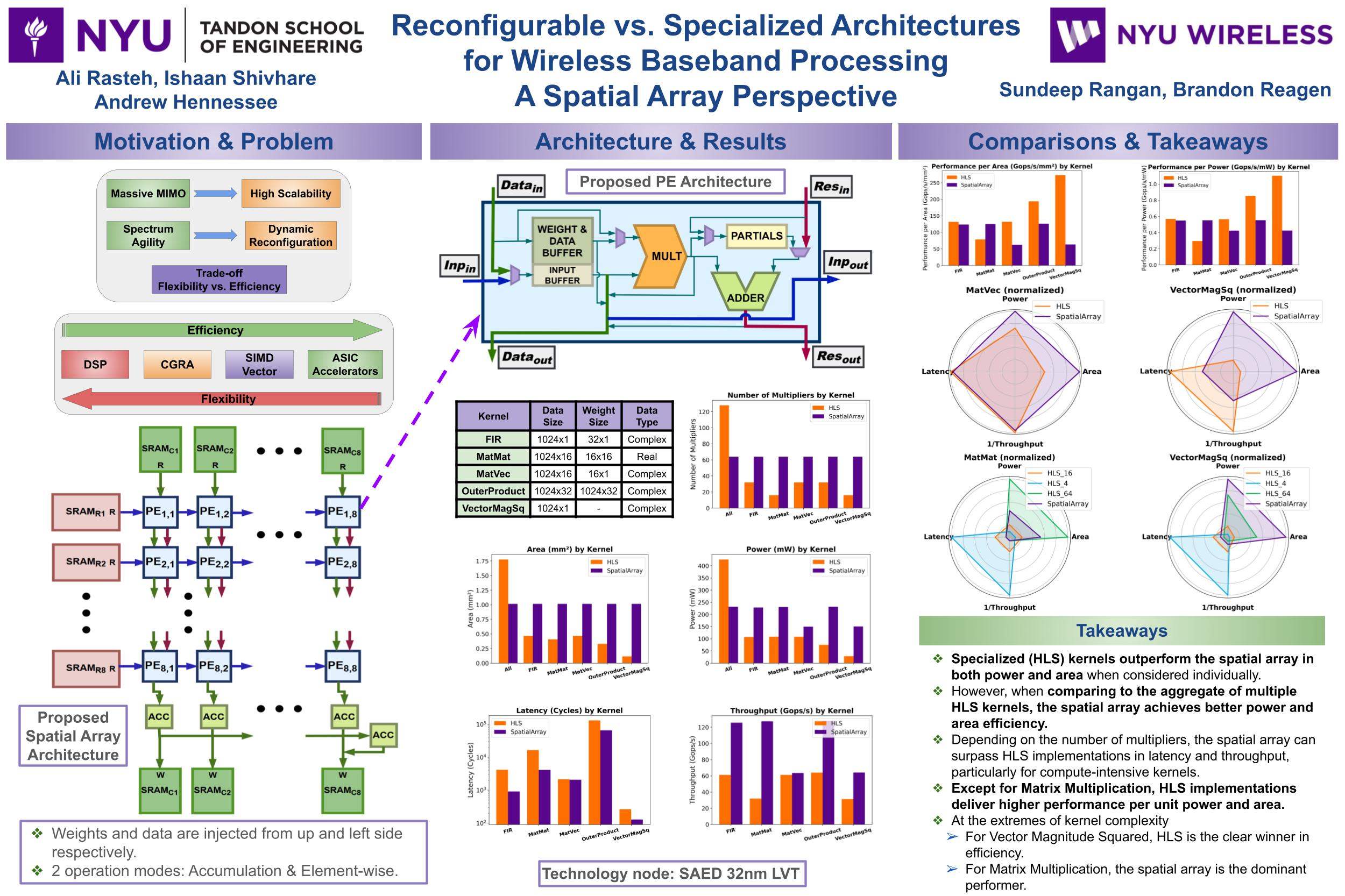

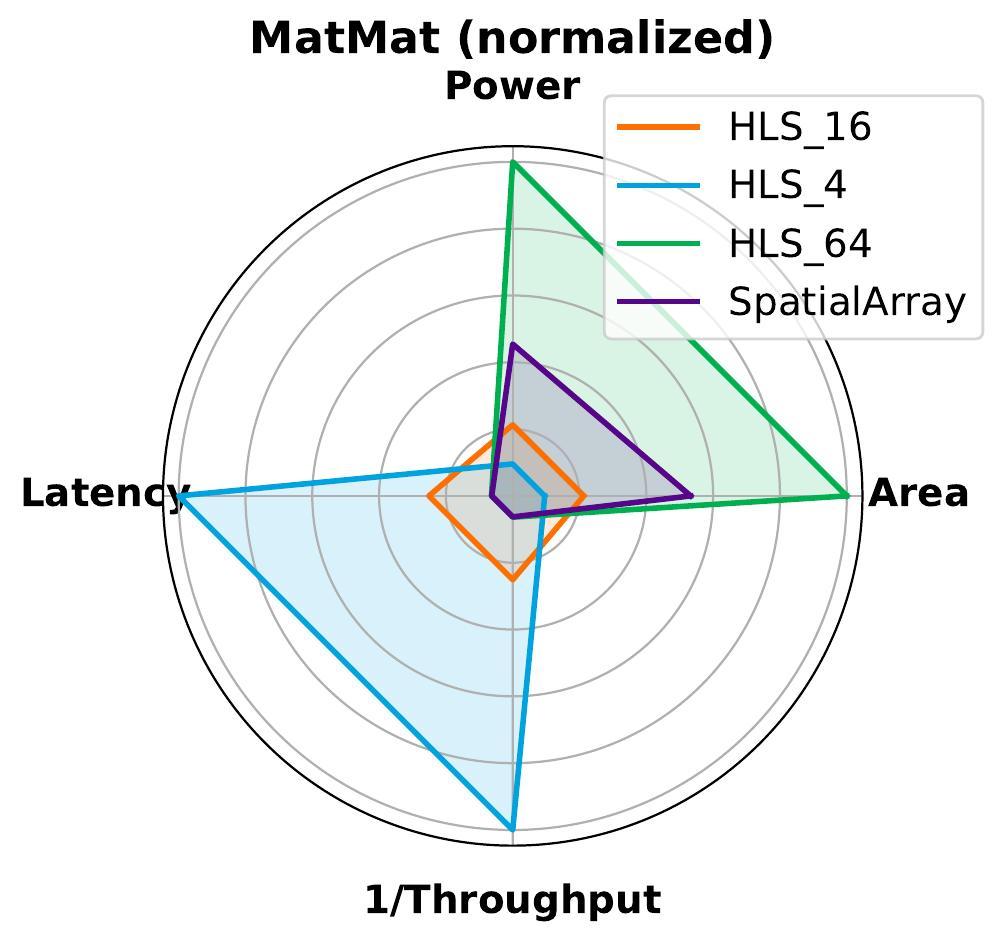

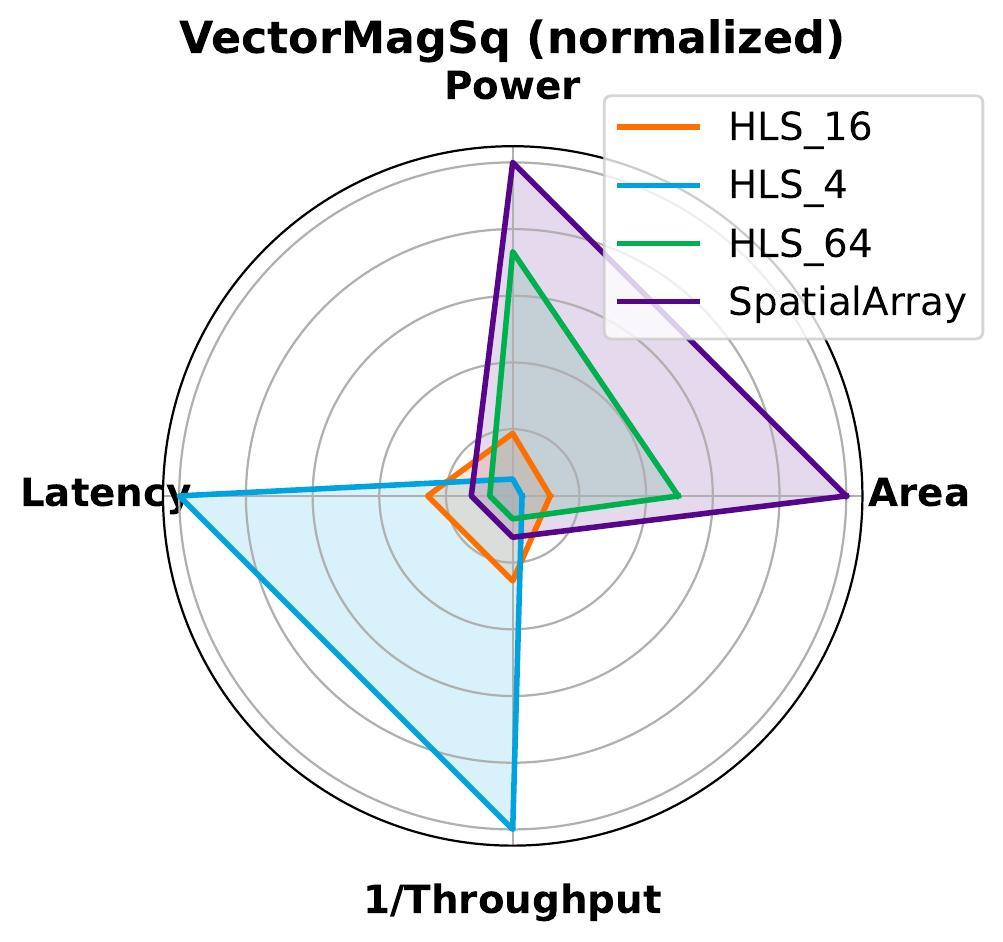

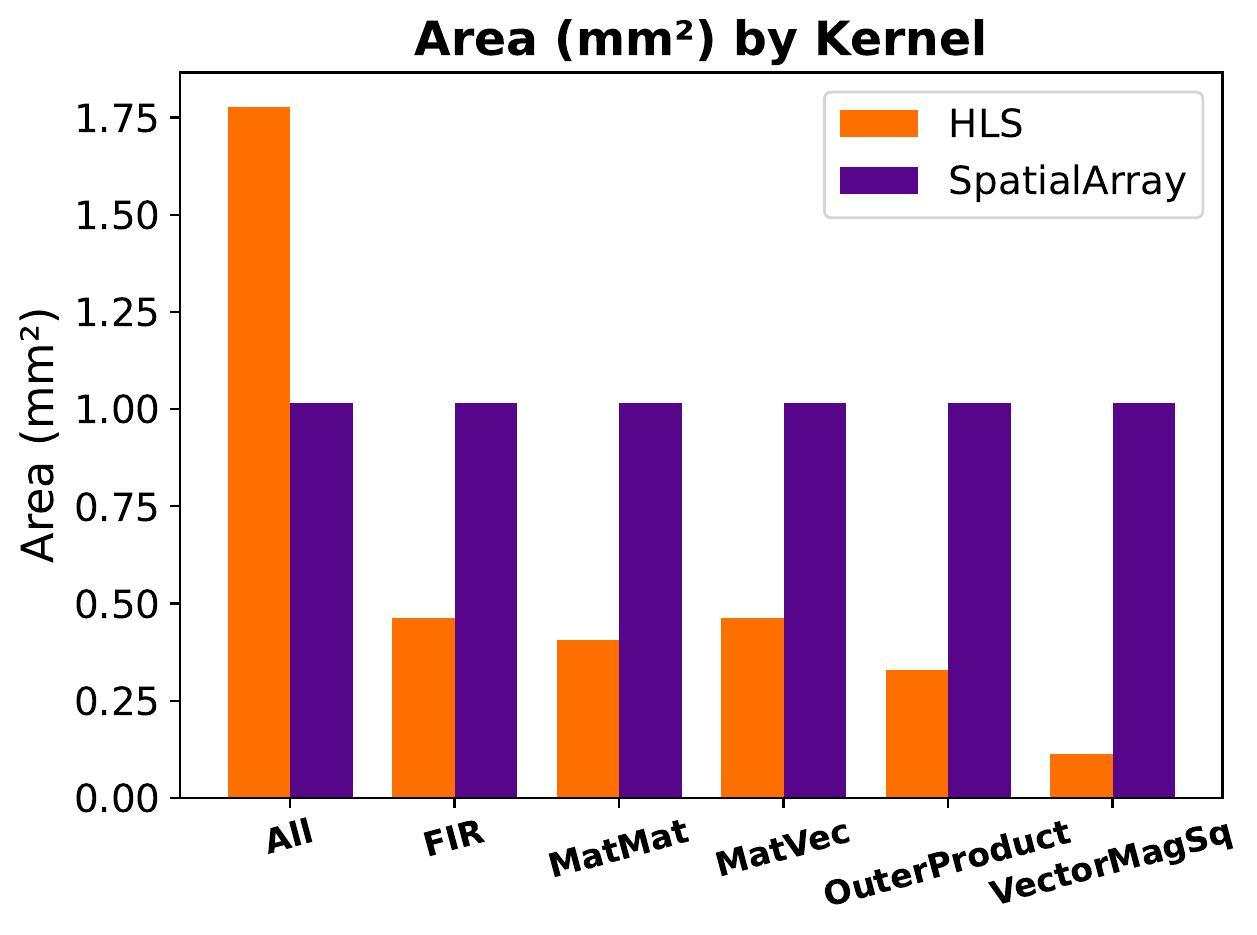

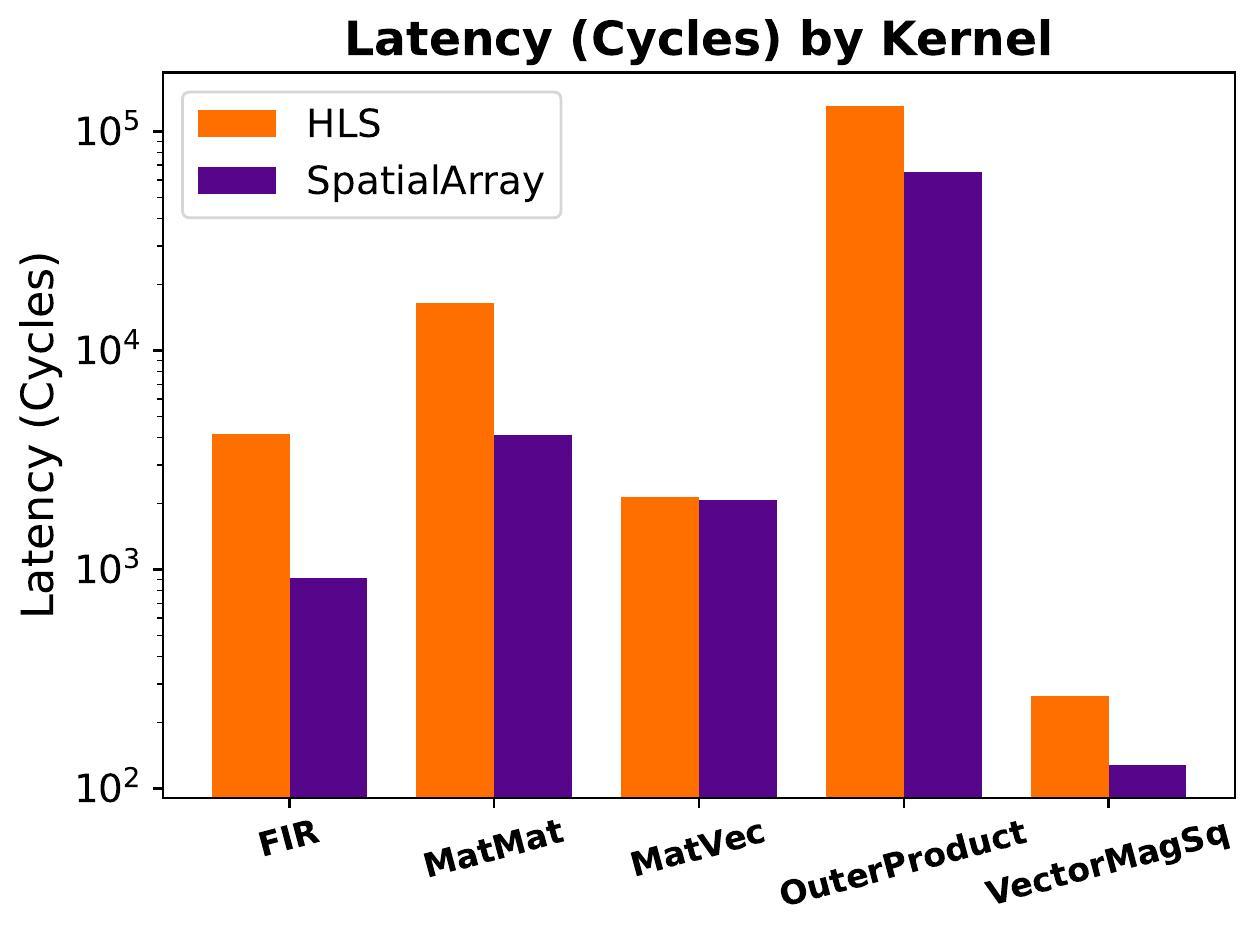

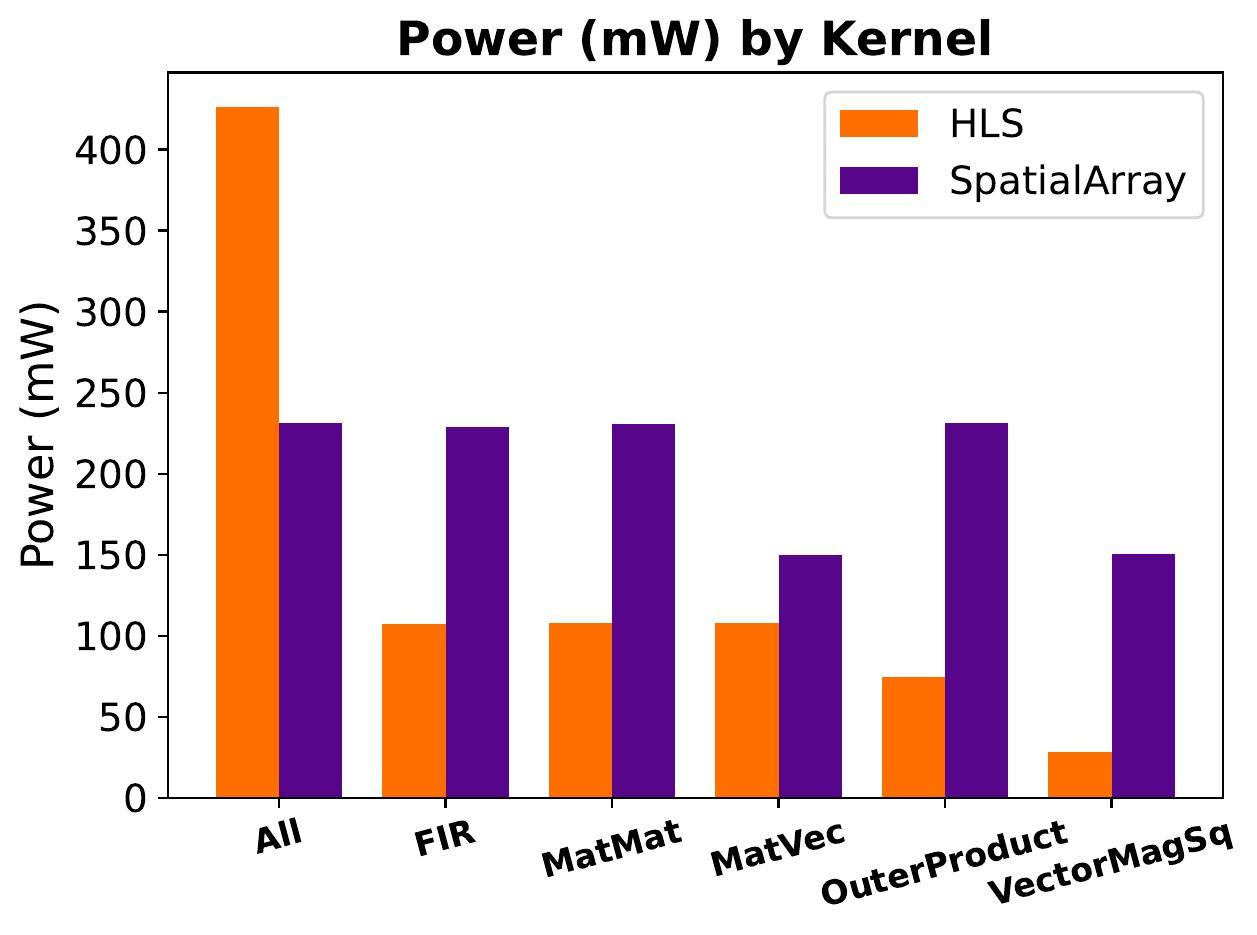

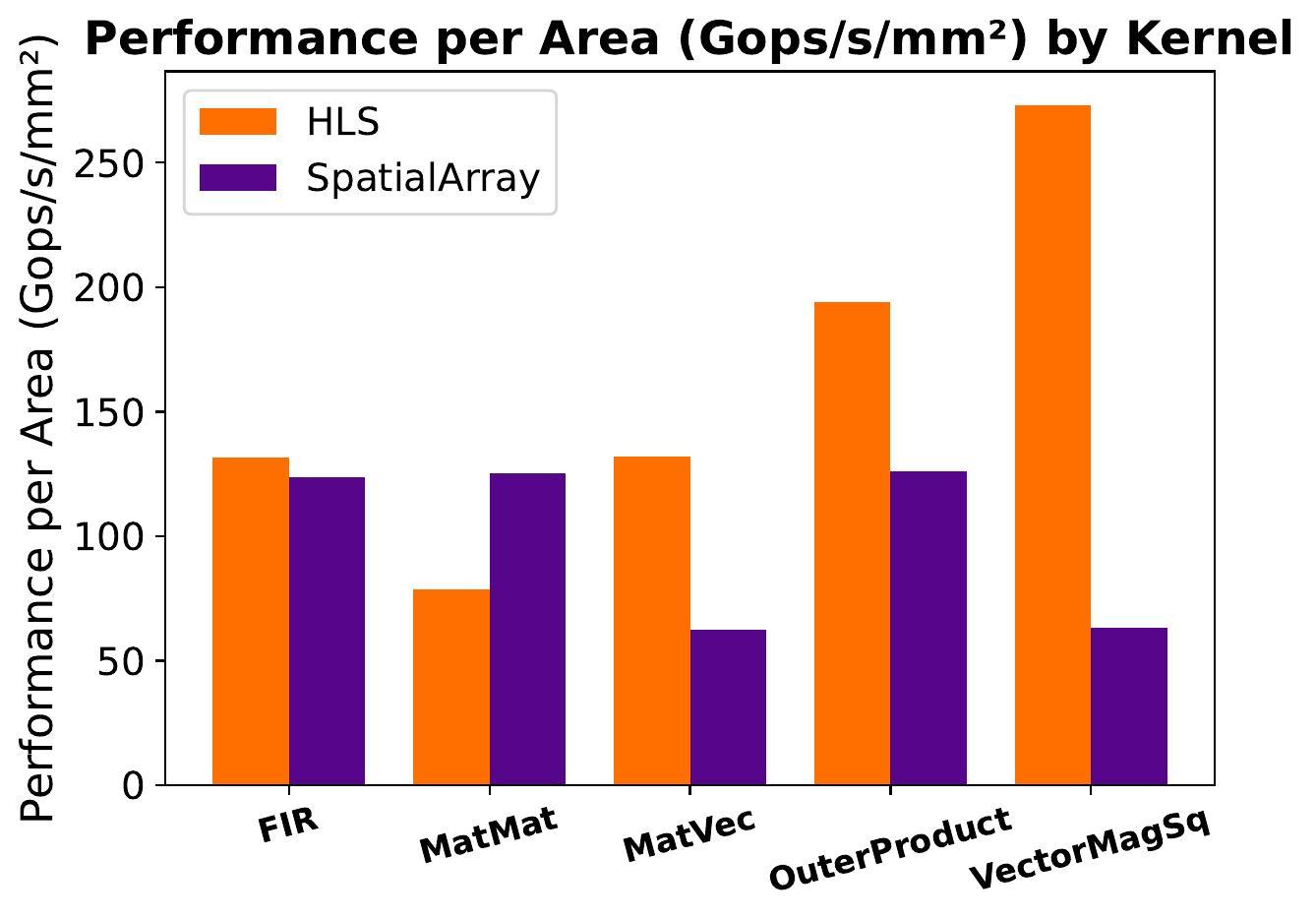

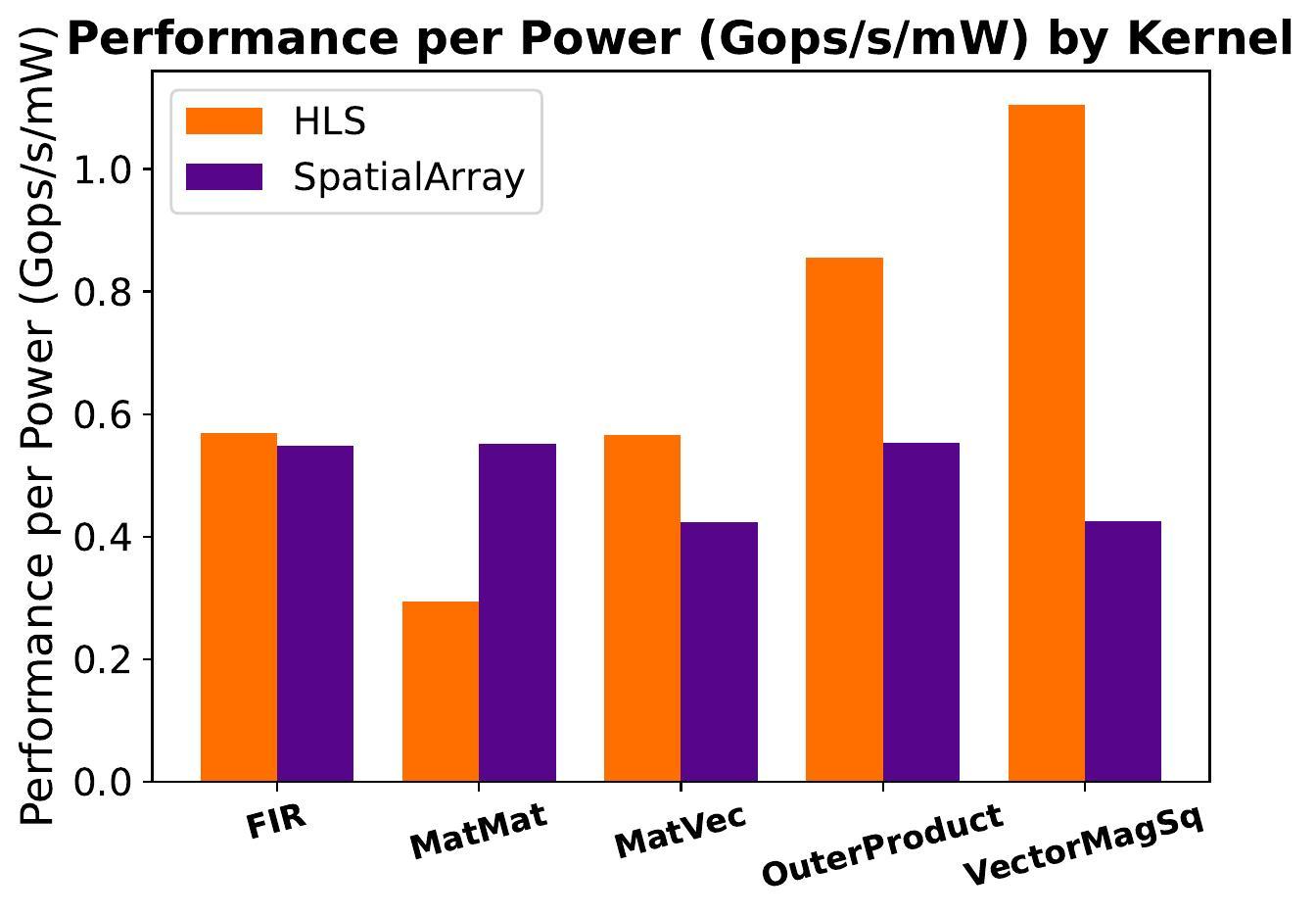

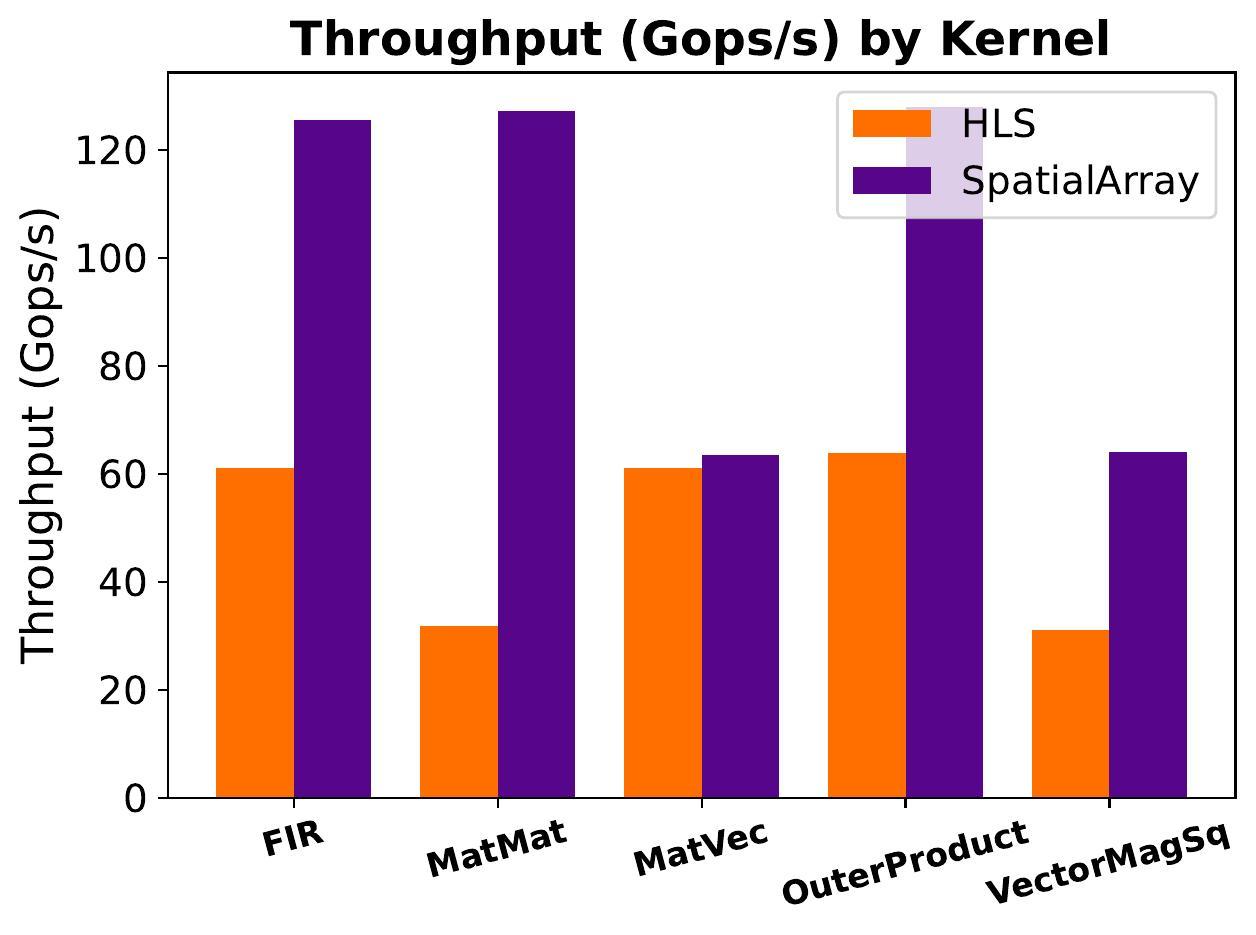

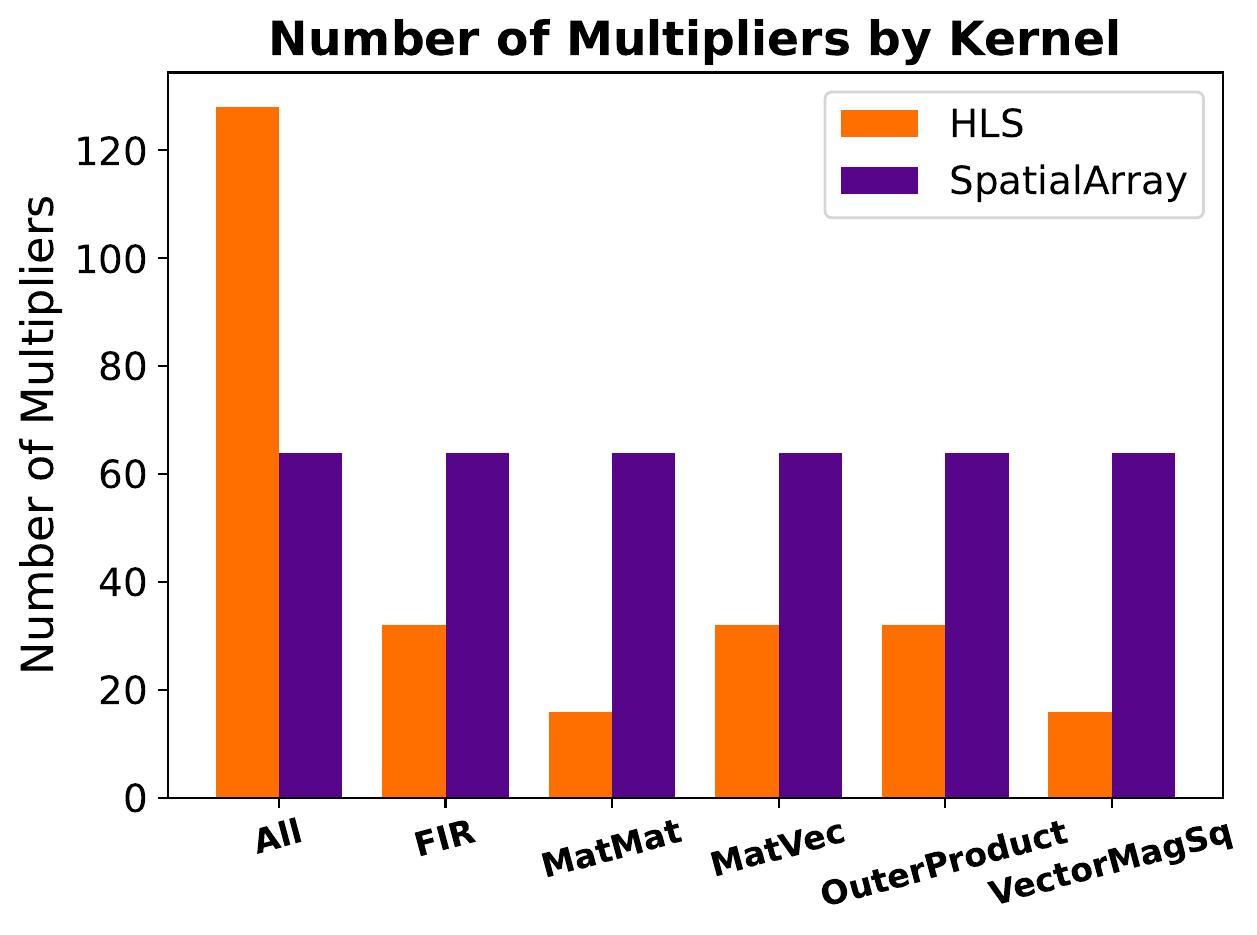

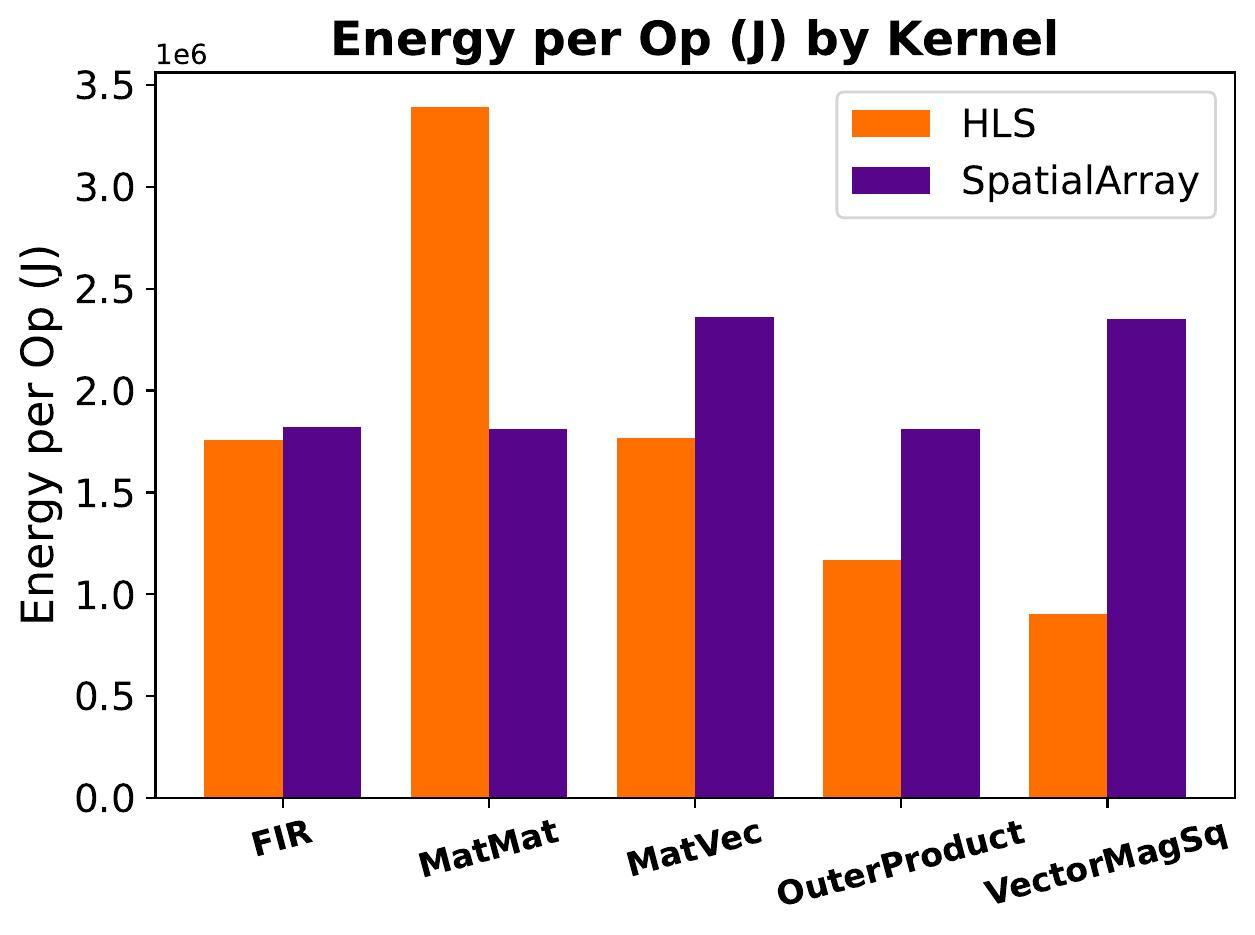

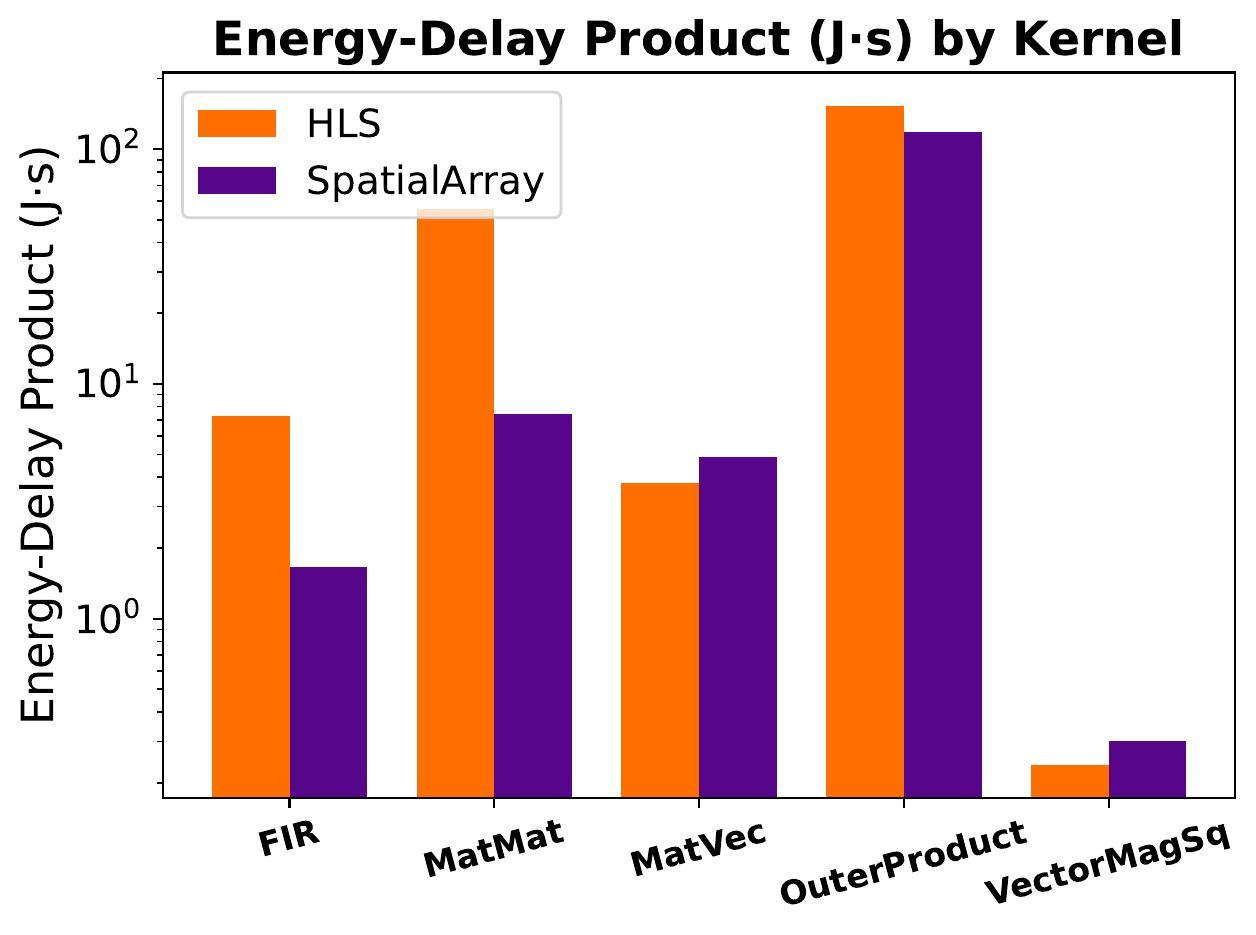

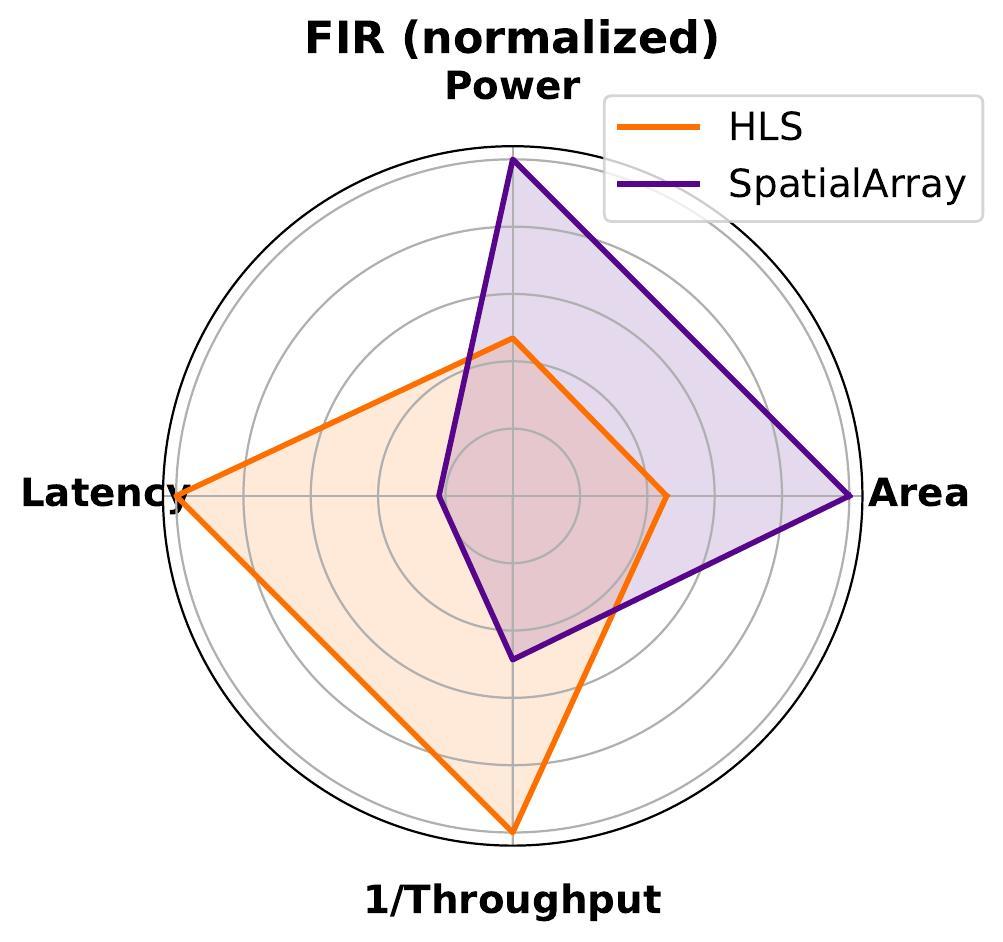

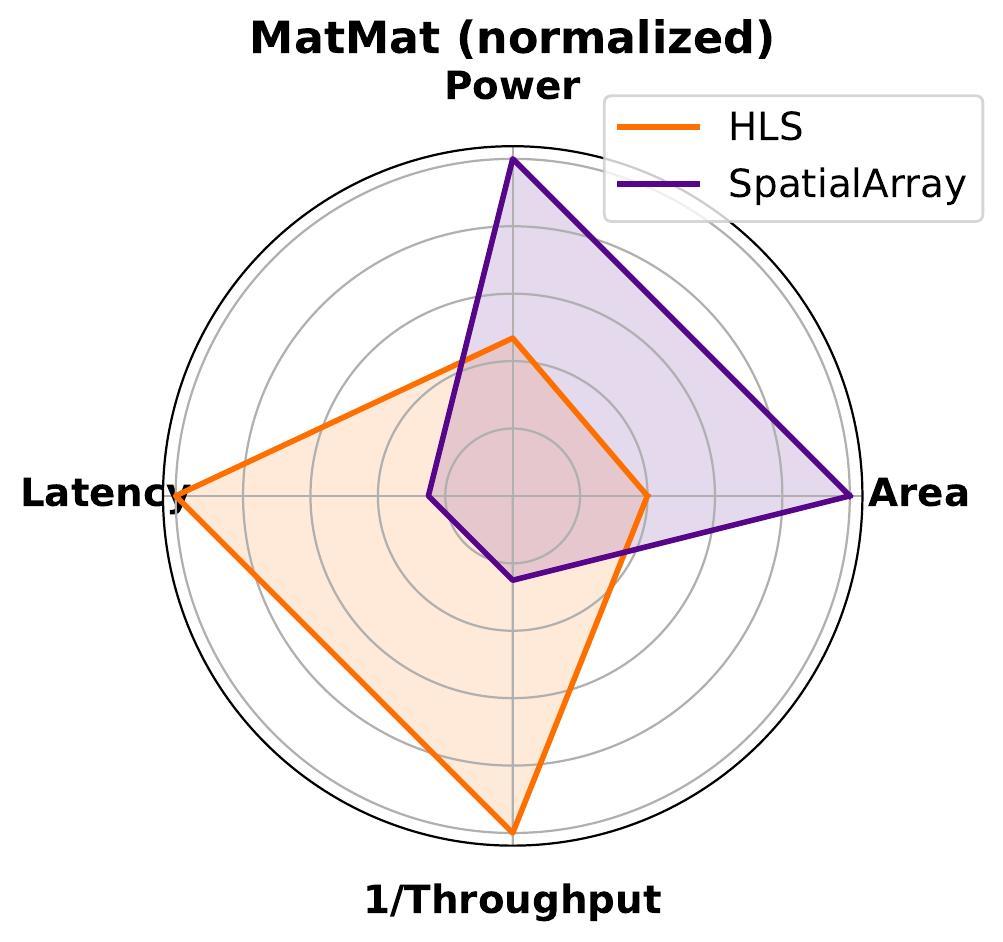

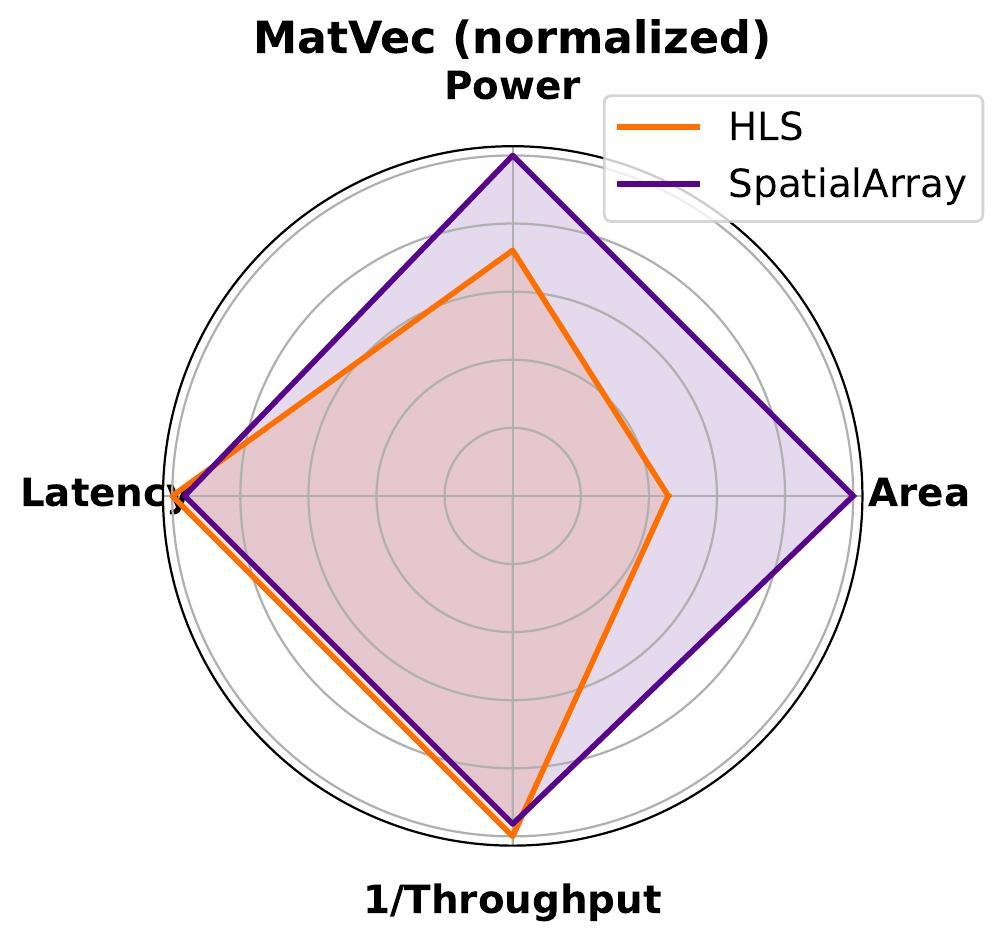

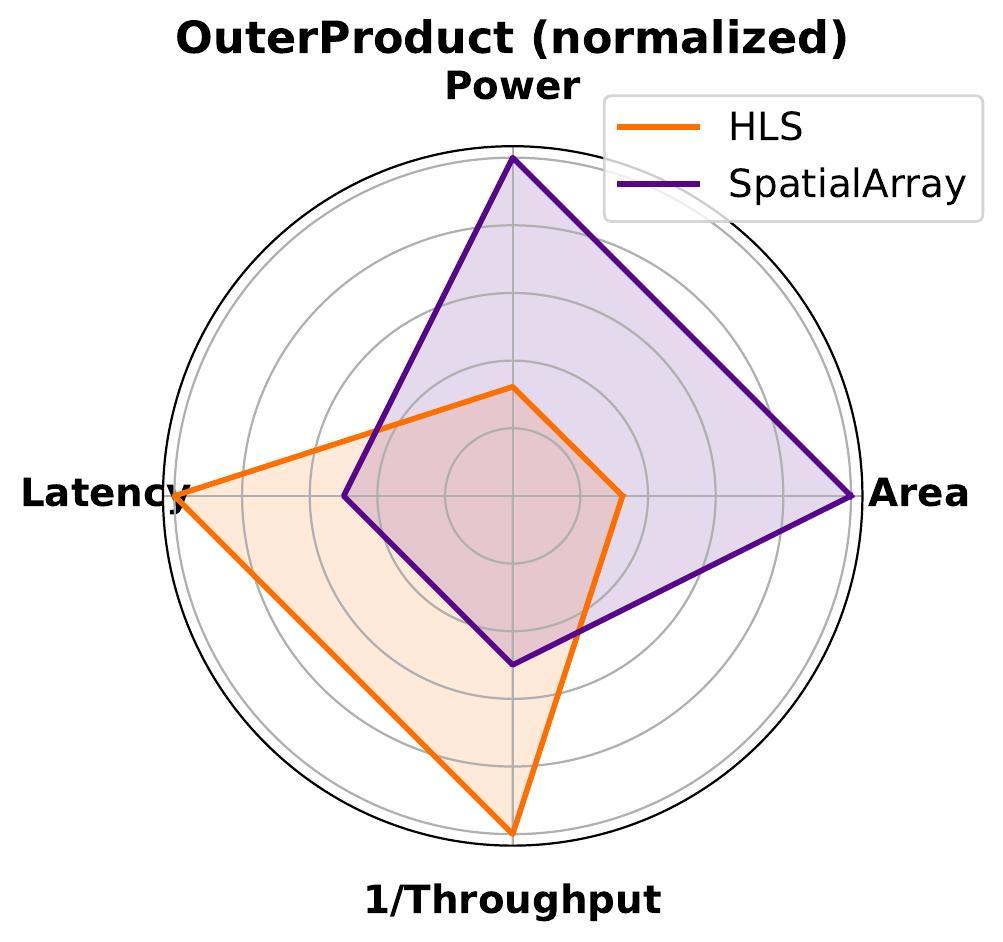

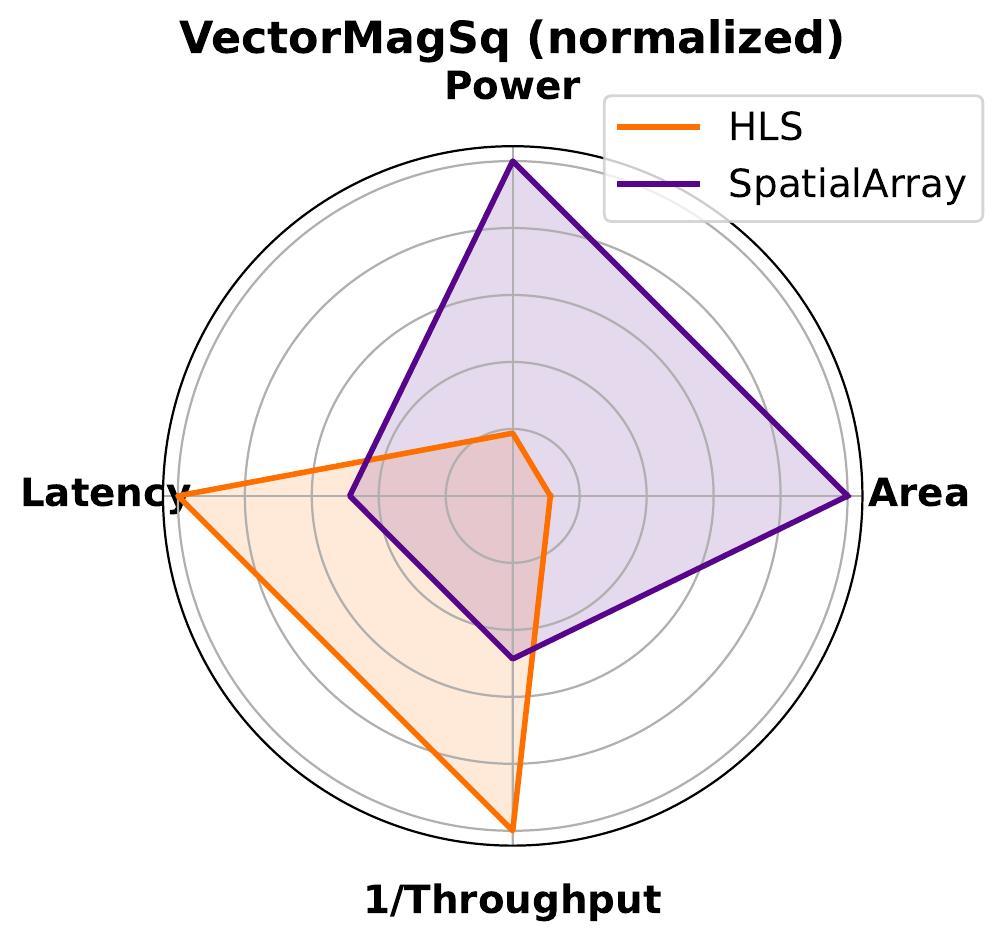

This paper presents a reconfigurable spatial array architecture designed to meet the scalability and spectral agility demands of next-generation massive MIMO and integrated sensing systems. The proposed architecture extends classical systolic arrays into a flexible, general-purpose compute engine capable of efficiently supporting a diverse set of wireless kernels, including matrix-matrix and matrix-vector multiplication, FIR filtering, matched filtering, outer products, and vector magnitude operations. The spatial array employs a weight-stationary dataflow, SRAM-connected rows and columns for adaptable data injection, and processing elements that support both accumulate and element-wise modes. This enables high data reuse and efficient mapping across communication and sensing workloads. The design was synthesized in a 32-nm technology node and evaluated against specialized High-Level Synthesis (HLS) hardware under identical memory bandwidth constraints. Experimental results demonstrate that while specialized HLS cores achieve better area and power efficiency for lightweight kernels, the spatial array delivers competitive performance and excels for compute-intensive workloads such as matrix multiplication. Importantly, a single spatial array can execute all evaluated kernels, whereas the HLS approach requires multiple dedicated cores to achieve the same functional coverage. This highlights a key advantage of the spatial array in reconfigurable systems. Overall, the work shows that general-purpose systolic architectures can closely approach the efficiency of specialized hardware while providing the flexibility required for scalable, spectrally agile wireless base stations and future integrated sensing and communication platforms.